全環(huán)繞柵極晶體管(GAAFET)

GAAFET的誕生

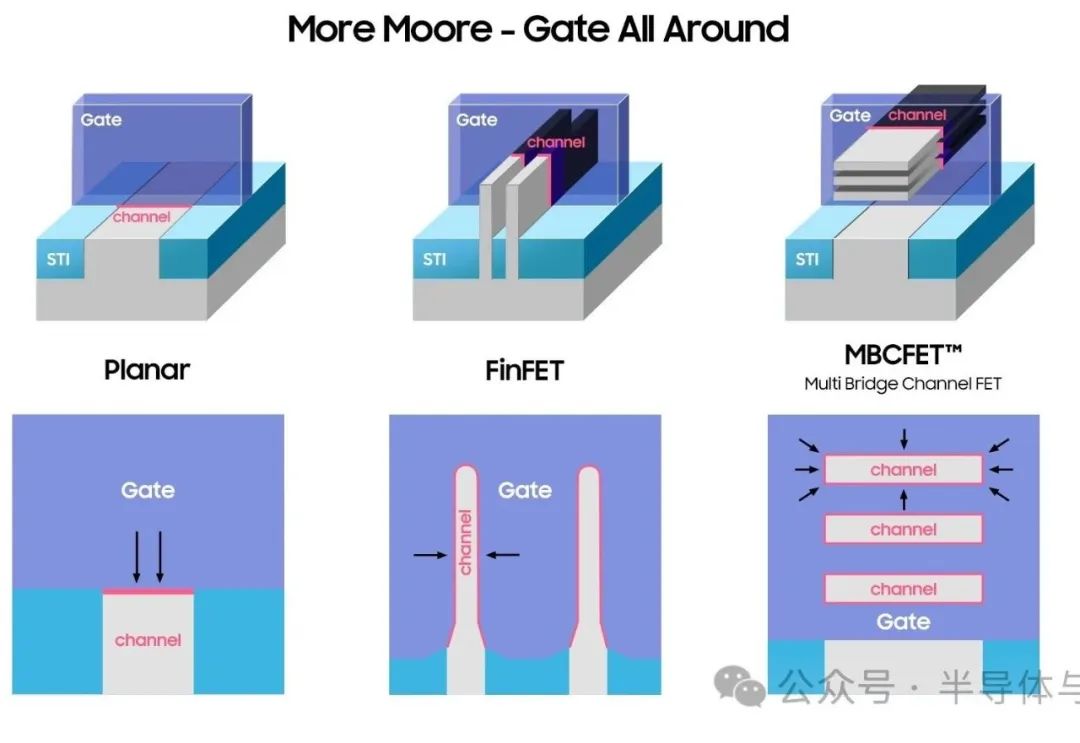

隨著半導(dǎo)體技術(shù)的發(fā)展,摩爾定律逐漸逼近物理極限。當(dāng)晶體管尺寸縮小到7納米以下時(shí),傳統(tǒng)的平面MOSFET和FinFET遇到了難以克服的技術(shù)瓶頸,如短溝道效應(yīng)(SCEs),這導(dǎo)致了漏電流增加、閾值電壓不穩(wěn)定等問(wèn)題。

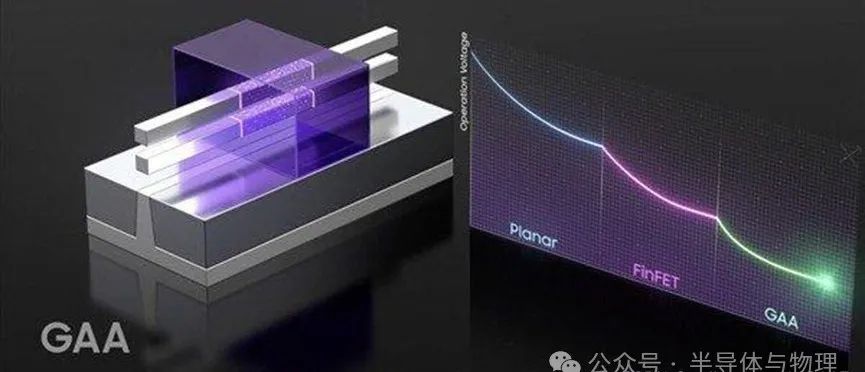

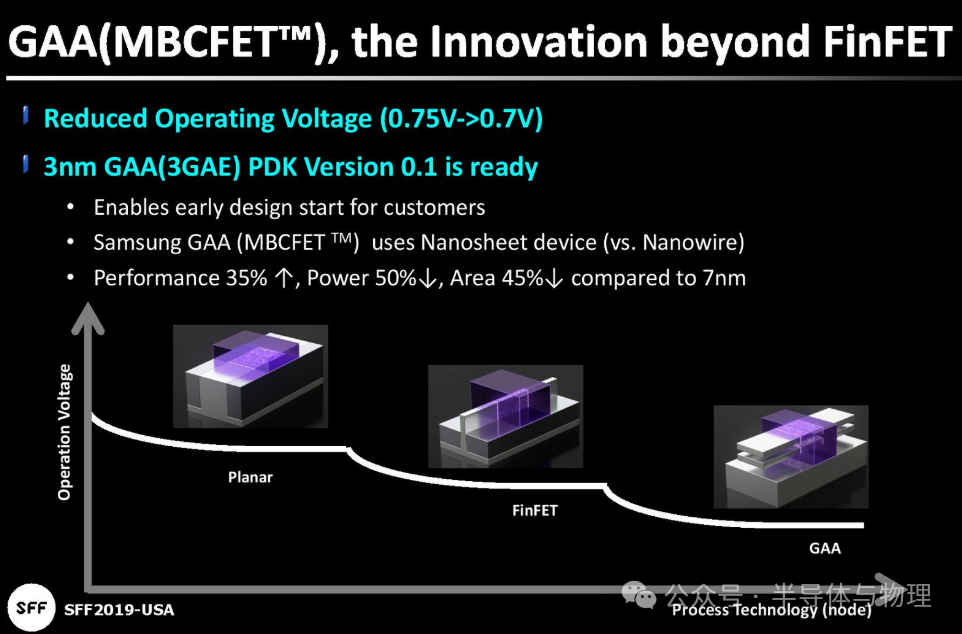

為了繼續(xù)實(shí)現(xiàn)邏輯縮放超越5納米技術(shù)節(jié)點(diǎn),并解決FinFET在進(jìn)一步縮小時(shí)遇到的問(wèn)題,行業(yè)開(kāi)始探索新的晶體管架構(gòu)——環(huán)繞柵極納米片場(chǎng)效應(yīng)晶體管(Gate-All-Around FET, GAAFET)。GAAFET通過(guò)提供更好的靜電控制和更高的性能密度,成為延續(xù)摩爾定律的關(guān)鍵。

為什么GAAFET比FinFET更好

更強(qiáng)的靜電控制:GAAFET的柵極圍繞著整個(gè)溝道四周,提供了全方位的靜電控制,有效地抑制了短溝道效應(yīng),降低了漏電流,并提高了閾值電壓的穩(wěn)定

相比之下,F(xiàn)inFET僅能在三個(gè)方向上控制溝道,而GAAFET實(shí)現(xiàn)了四面環(huán)繞控制,使得溝道電流更加順暢。

更高的驅(qū)動(dòng)電流:相較于FinFET,GAAFET可以支持更寬的溝道寬度,即柵極打開(kāi)狀態(tài)下的電流更大,從而提升了晶體管的開(kāi)關(guān)速度和整體性能。對(duì)于納米線結(jié)構(gòu)而言,雖然其柵控能力不如納米片強(qiáng),但能夠承載更大的電流;而對(duì)于納米片結(jié)構(gòu)(如三星的MBCFET),則可以在更小面積內(nèi)提供更好的靜電特性,滿足某些柵極寬度的需求

更好的可擴(kuò)展性:由于GAAFET的溝道厚度不是通過(guò)光刻定義而是通過(guò)外延生長(zhǎng)定義的,這使得它在進(jìn)一步縮小尺寸方面具有更大的靈活性和潛力,不受傳統(tǒng)圖案化分辨率的限制

多層堆疊設(shè)計(jì):GAAFET允許將多個(gè)納米片垂直堆疊在一起形成一個(gè)器件,這不僅增加了有效溝道面積,還能夠優(yōu)化空間利用率,提高集成度。這種設(shè)計(jì)為未來(lái)的高密度集成電路提供了可能

GAAFET的制造大概流程

GAAFET的制造涉及到一系列復(fù)雜的工藝步驟,下面簡(jiǎn)要介紹其主要流程:

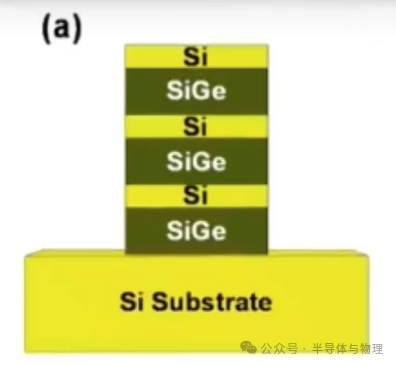

堆疊納米片形成:首先,在硅襯底上交替沉積SiGe和Si層,形成多層結(jié)構(gòu)。這些材料的選擇性生長(zhǎng)確保了每一層的精確控制,最終構(gòu)成所需的納米片結(jié)構(gòu)。這一過(guò)程利用了超晶格結(jié)構(gòu)(super-lattice),每種材料疊多層,sheet就是在超晶格結(jié)構(gòu)中形成的。

鰭片顯露與淺溝槽隔離(STI):接下來(lái),利用光刻技術(shù)定義出各個(gè)器件區(qū)域,并進(jìn)行淺溝槽隔離處理以隔離相鄰器件,保證它們之間不會(huì)互相干擾。這一步驟對(duì)于確保每個(gè)晶體管獨(dú)立工作至關(guān)重要。

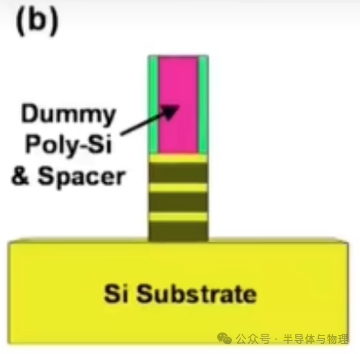

虛擬柵極形成:在此階段,會(huì)形成一個(gè)臨時(shí)性的Si3N4虛擬柵極,用于支撐后續(xù)的加工過(guò)程。這個(gè)虛擬柵極將在后續(xù)步驟中被替換為實(shí)際的金屬柵極。

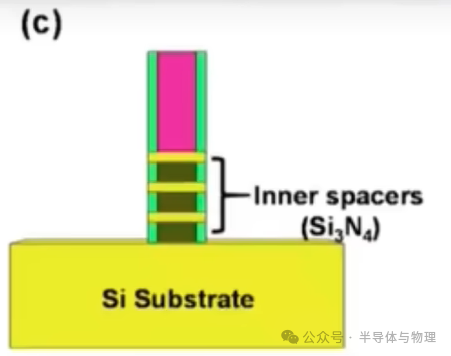

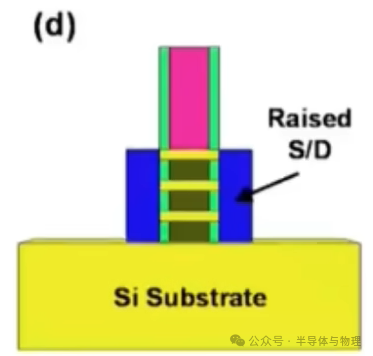

內(nèi)間隔物及源/漏區(qū)形成:在暴露出來(lái)的納米片兩端選擇性地生長(zhǎng)n型或p型摻雜的源/漏區(qū),同時(shí)形成內(nèi)間隔物來(lái)保護(hù)納米片并為之后的金屬柵極填充做準(zhǔn)備。內(nèi)間隔物的作用在于防止柵極與源漏之間的短路。

替換金屬柵極形成:

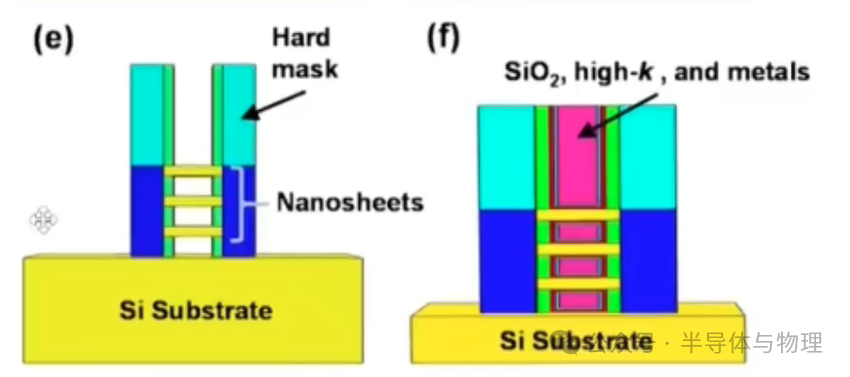

犧牲SiGe通道釋放:去除納米片間的SiGe層,以便于填充高k金屬柵極材料;

高k金屬柵極(HKMG)形成:依次沉積界面氧化物、高k電介質(zhì)層以及金屬,構(gòu)建完整的柵極結(jié)構(gòu)。高k金屬柵極的應(yīng)用增強(qiáng)了柵極對(duì)溝道的控制力,減少了寄生電容的影響。

參考文獻(xiàn):

[1] Mukesh, S., & Zhang, J. (2022). A review of the gate-all-around nanosheet FET process opportunities. Electronics, 11(21), 3589.

[2] 3D IC devices, technologies, and manufacturing / Hong Xiao.